Fault-tolerant FPGA Architecture

A Self-Repairing Bio-Inspired Fault-Tolerant FPGA Architecture

Role: Research Assistant, Sole Developer/Designer.

Tools and skills used: Xilinx Virtex-5 FPGA, Xilinx ISE Toolchain, Verilog HDL, ModelSim, LabVIEW.

About:

The mitigation of single-event upsets (SEUs) through modular or functional redundancy is a traditional approach for designing fault-tolerant systems; however, even in multiple redundant systems, SEUs can lead to a system failure if they occur simultaneously. Previous fault-tolerant approaches have proposed run-time reconfiguration to regain the lost functionality.

A similar strategy is adopted to overcome failures caused by unidirectional SEUs occurring simultaneously in both frontline and redundant modules, but the approach proposed in this work not only improves reliability but also requires low area-overhead as compared to previous methodologies.

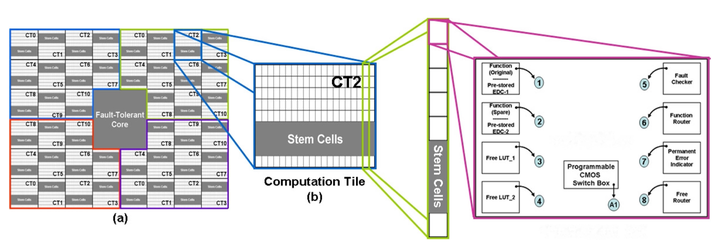

The proposed architecture is an array of computation tiles containing computation cells and corresponding hot-spares. Each computation tile has a separate region for spare cells. The simultaneous faults are handled by an on-chip fault-tolerant core and external host software that partially reconfigure the spare-cells region of a computation tile.

The proposed architecture is implemented on a Xilinx Virtex-5 FPGA device and verified with the aid of simple digital application. Compared to previous schemes, our approach requires up to 9.6x less area overhead while providing 57.6% more reliability to mask multiple unidirectional SEUs.

The video demonstration of this project with a simple example is shown below: