Fault-Tolerant RISC-V Processor

Role: BE Thesis Supervisor.

Tools and skills used: Xilinx ZEDboard, ARM processor, FPGA, XILINX Vivado, ModelSim, Verilog HDL.

About:

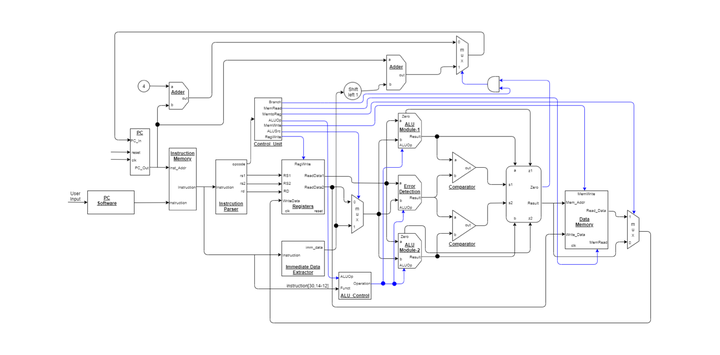

This project goal was to implement a subset of RISC-V processor on FPGA and make it fault-tolerant. The key features of the project include the implementation of RISC-V on FPGA which offers the advantage of reduced and simple instructions set. Additionally, a fault-tolerant ALU for architecture is another key feature for error-free applications.