Measurement of On-Chip Speed/Thermal Variations

A Novel Automated Experimental Approach for the Measurement of On-Chip Speed Variations through Dynamic Partial Reconfiguration

Role: MS student, Sole Developer.

Tools and skills used: Xilinx Virtex-5 FPGA, Microblaze microprocessor, Xilinx ISE Toolchain, ModelSim, Verilog HDL.

About:

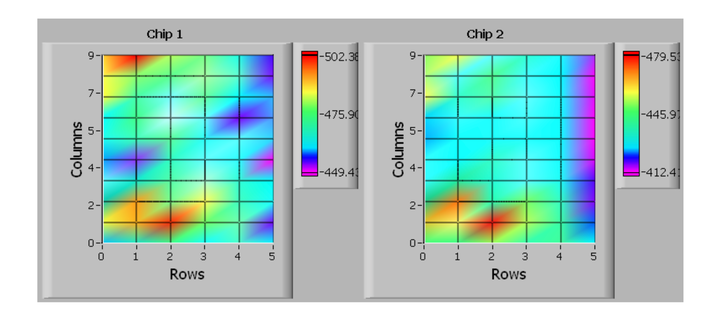

In this research, a complete automated experimental setup for the measurement of on-chip delay variations through dynamic partial reconfiguration was developed. The experiment was performed on two same Virtex-5 (XC5VLX110T) devices on the basis of which intra-die and inter-die speed comparisons were made. On-chip sensor map was developed, consists of 60 sensors out of which only alternating sensors remains active at a time. This is done to avoid neighboring sensors heat dissipation. Host GUI was developed on LabVIEW platform which monitors and supervises the whole process running on chip. GUI allows user to load partial bitstream of any sensor map. While maintaining the sensor topology constant, we found the intra-die speed variations up to 6-10%. However, inter-die speed comparison result depicts that one chip is 2-10% faster than another one.